명령어의 처리 과정은 컴퓨터의 기본 동작 단계로, CPU가 명령어를 가져와 해독하고 실행하는 과정을 포함한다. CPU는 여러 구성 요소와 기능으로 이루어져 있으며, 명령어 처리에는 다양한 단계와 구성 요소들이 관련되어 있다.

CPU 구조와 기능:

1. 레지스터:

레지스터는 CPU 내부에 있는 속도가 빠른 메모리로, 명령어를 저장하고 처리하는데 사용된다. 이 중 중요한 레지스터에는 다음과 같은 것들이 있다.

누산기 (Accumulator)

- 1주소 명령어를 사용하는 시스템에서 연산의 중심이 되는 레지스터이다.

- 연산 결과를 일시적으로 저장하거나 중앙에서 다른 레지스터로 전송된다.

범용 레지스터 (General-purpose Register)

- 산술 및 논리 연산, 연산 결과의 임시 저장, 주소 색인 등 다양한 목적으로 사용되는 레지스터이다.

- 2주소 명령어나 3주소 명령어를 사용하는 시스템에서는 CPU 내에 여러 개의 범용 레지스터를 보유한다.

프로그램 카운터 (Program Counter)

- 다음에 수행될 명령어가 저장된 주소를 가리키는 레지스터이다.

- 현재 명령어의 주소를 지시하고, 다음 위치로 이동하기 위해 내용이 하나 증가된다.

명령어 레지스터 (Instruction Register)

- 실행될 명령어를 일시적으로 보존하는 레지스터이다.

- 명령어를 받은 후 제어 유닛으로 보내어 실행 준비를 한다.

주소 레지스터 (Memory Address Register)

- CPU에 저장된 명령어의 주소를 일시적으로 저장하는 레지스터이다.

- 프로그램 카운터(PC)의 값이 이곳으로 옮겨지며, 주소 버스와 연결되어 시스템 주소 버스로 출력된다.

메모리 버퍼 레지스터 (Memory Buffer Register)

- 주소 레지스터(MAR)가 가리키는 주소 위치의 내용(명령어 또는 데이터)을 일시적으로 저장하는 레지스터이다.

- 명령어는 명령어 레지스터(IR)로, 데이터는 다른 레지스터(예: AC, R1, R2 등)로 옮겨진다.

- 데이터 버스와 연결되어 데이터 전송을 담당한다.

2. 산술 논리 장치(ALU, Arithmetic Logic Unit):

ALU는 CPU의 중요한 부분 중 하나로, 산술 연산과 논리 연산을 수행한다.

2진의 가감산: ALU는 덧셈과 뺄셈을 비롯한 기본적인 산술 연산을 수행한다. 두 개의 이진 수를 더하거나 빼는 것이 가능하다.

논리 연산: AND, OR, NOT, XOR 등의 논리 연산을 수행할 수 있다. 이러한 논리 연산은 불(bool) 값에 대한 연산을 실행하며, 데이터의 비트 단위로 연산을 수행한다.

보수 연산: 보수 연산은 특히 이진수에 적용되며, 1의 보수와 2의 보수를 계산하는 등의 작업을 수행한다. 보수 연산은 음수를 나타내는 데 사용되기도 한다.

Shift right & Shift left: ALU는 비트를 오른쪽 또는 왼쪽으로 이동시키는 기능을 수행한다. Shift right는 비트를 오른쪽으로 이동시키며, Shift left는 비트를 왼쪽으로 이동시킨다.

3. 제어 장치(Control Unit):

명령어 해석 및 실행 제어:

- 프로그램 코드(명령어)를 해독하고 실행하기 위한 제어 신호를 생성한다.

- 명령어를 해독하여 해당하는 하드웨어 구성 요소로 전달하여 실행할 수 있도록 한다.

CPU 내부 버스 및 하드웨어 제어:

- CPU 내부의 버스를 제어하고, ALU(산술 논리 장치)와 레지스터 등과 같은 하드웨어 장치 간의 데이터 전송 및 연산에 필요한 동작 신호를 전송한다.

- ALU가 수행해야 하는 산술 및 논리 연산을 위해 필요한 제어 신호를 생성하고 전송한다.

외부 메모리 및 I/O 버스 제어:

- CPU와 외부 메모리 간의 데이터 전송을 위해 읽기(read)와 쓰기(write) 신호를 생성하여 외부 메모리와의 통신을 관리한다.

- I/O 버스와의 통신을 위해 필요한 신호들을 생성하여 데이터의 입출력을 관리한다.

명령어 처리 단계:

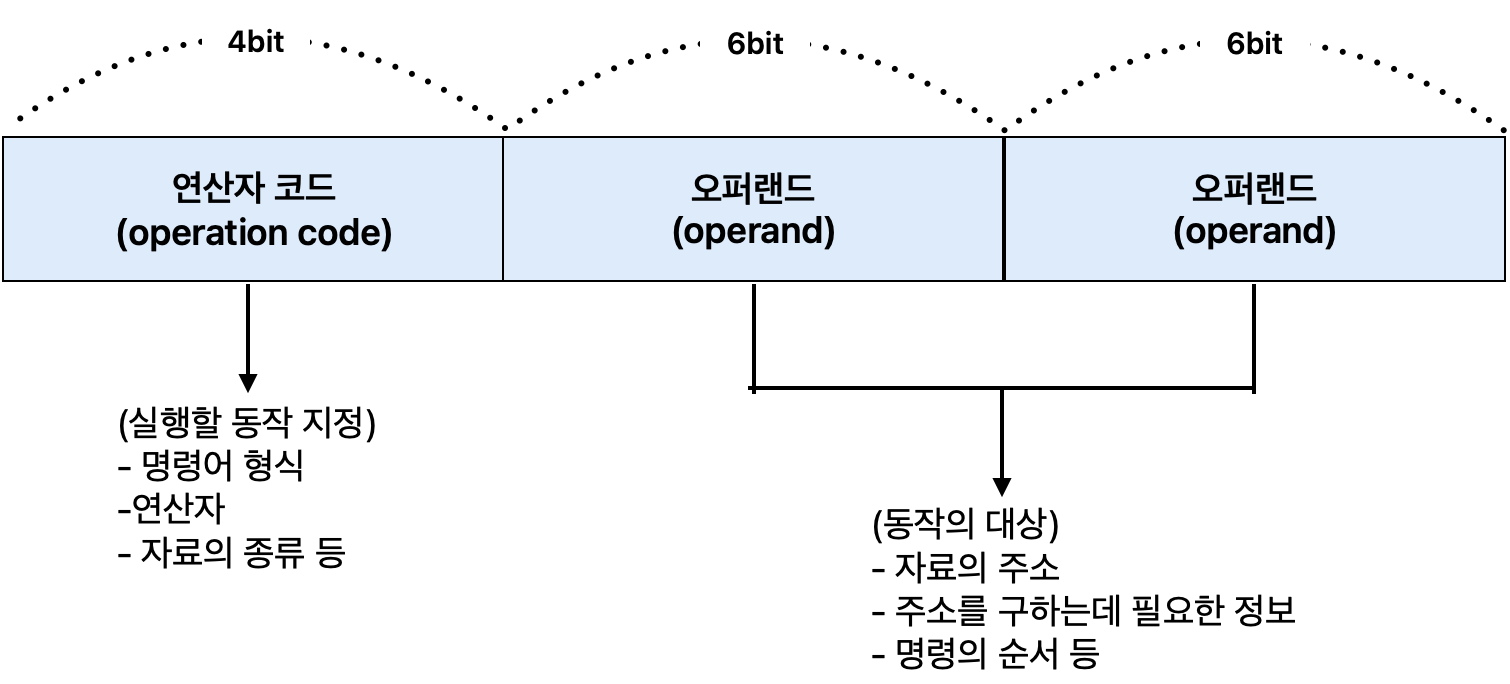

명령어의 형식은 컴퓨터가 명령어를 해독하고 실행하는 데 필요한 구조를 나타낸다. 일반적으로 명령어는 연산 코드(Operation code)와 오퍼랜드(operand)로 구성되어 있다.

명령어의 구성:

- 연산 코드(Operation code): 명령어에서 수행할 동작을 정의하는 부분으로, 사칙 연산이나 보수 연산 등의 동작을 나타낸다.

- 오퍼랜드(Operand): 주기억장치의 데이터 번지, 명령 번지, 보조기억장치의 데이터 번지 또는 명령 번지 등 데이터를 다루는 부분이다.

주소에 따른 명령어 형식:

0-주소 명령어

- 연산 결과를 고정된 장소에 기억하는 명령어 형식이다.

- 스택을 사용하여 연산을 수행하고, 모든 연산은 스택에 있는 자료를 활용한다.

- 예시: PUSH A, PUSH B, ADD (연산자 없이 스택에 있는 피연산자들을 더함)

1-주소 명령어

- 한 개의 오퍼랜드를 포함하는 명령어 형식이다.

- 예시: ADD X (AC ← AC + M[X], M[X]는 기억장치 X 번지의 내용을 의미)

2-주소 명령어:

- 두 개의 오퍼랜드를 가진 명령어 형식이다.

- 예시: ADD R1, R2 (R1 ← R1 + R2), MOV R1, R2 (R1 ← R2)

3-주소 명령어:

- 세 개의 오퍼랜드로 구성되며, 여러 개의 범용 레지스터를 사용하는 형식이다.

- 장점은 수식 계산 후에도 입력 자료가 보존 가능하며, 프로그램 길이를 절감할 수 있다. 단점으로는 최소한 4번 기억 장치에서 액세스하므로 수행시간이 지연되고 명령어 해독 과정이 복잡해질 수 있다.

명령어 사이클

명령어 사이클은 CPU가 명령어를 실행하는데 필요한 전체 처리 과정을 나타내며, CPU가 프로그램을 실행하는 동안 반복된다. 이것은 CPU가 전원을 켠 순간부터 전원을 끄거나 회복 불가능한 오류가 발생할 때까지 명령어를 불러오고 실행하는 과정을 의미한다.

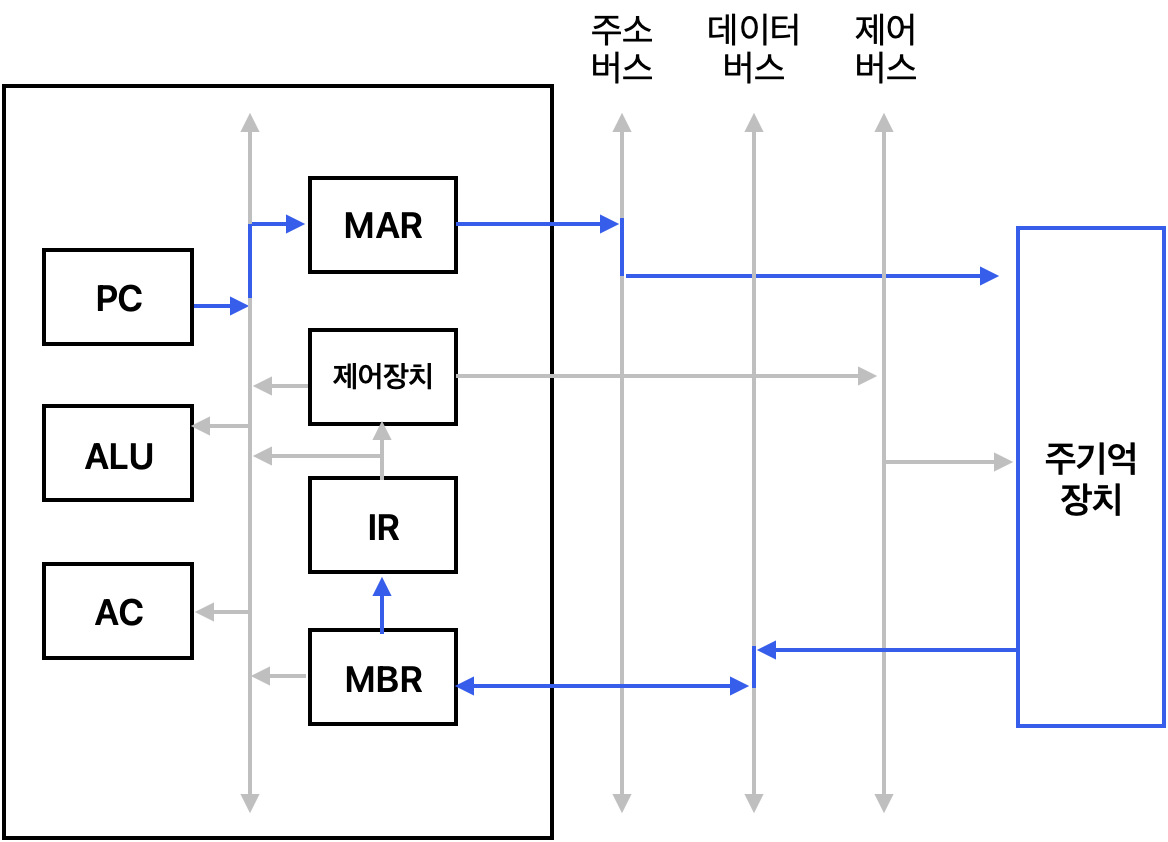

인출 사이클 (Fetch Cycle)

- CPU가 기억장치로부터 명령어를 읽어오는 단계

- 마이크로 연산:

- MAR ← PC: 현재 PC(Program Counter)에 저장된 명령어 번지를 MAR(Memory Address Register)로 전송한다.

- MBR ← M[MAR], PC ← PC+1: MAR 번지의 명령어를 MBR(Memory Buffer Register)로 읽어오고, PC를 다음 명령어 번지로 증가시킨다.

- IR ← MBR: 메모리에서 읽어온 명령어를 IR(Instruction Register)로 전송하여 해독 준비를 한 다.

간접 사이클 (Indirect Cycle)

- 오퍼랜드 필드에 포함된 간접주소로부터 실제 피연산자가 저장된 위치를 가리키는 유효주소를 읽어들이는 단계

- 마이크로 연산:

- MAR ← IR(오퍼랜드): 오퍼랜드 필드에 있는 간접 번지를 MAR로 전송한다.

- MBR ← M[MAR]: MAR 번지의 유효주소를 MBR로 읽는다.

- IR(오퍼랜드) ← MBR: MBR의 내용을 IR(오퍼랜드)로 전송하여 실제 피연산자를 가리키는 유효주소를 사용 가능하게 준비한다.

실행 사이클 (Execution Cycle)

- CPU가 인출된 명령어 코드를 해독하고 필요한 연산을 수행하는 단계

실행 사이클 처리 과정:

1. 명령어 인출 (Instruction Fetch):

- 기억장치로부터 명령어를 읽어온다.

- PC(Program Counter)가 가리키는 메모리 주소에서 명령어를 인출하여 다음 실행할 명령어의 위치를 결정한다.

2. 명령어 해독 (Instruction Decode):

- 명령어를 해독하여 수행해야 할 동작을 결정한다.

- 해당 명령어가 어떤 연산을 수행해야 하는지 파악하고, 그에 따른 제어 신호를 생성한다.

3. 데이터 인출 (Data Fetch):

- 명령어 실행에 필요한 데이터가 기억장치나 입출력 장치 등에서 필요한 경우 해당 데이터를 인출한다.

- 명령어 실행에 필요한 데이터를 메모리나 다른 장치로부터 가져와 레지스터나 연산 장치에 제공한다.

4. 데이터 처리 (Data Process):

- 수행해야 할 연산에 따라 데이터에 대한 산술적 또는 논리적 연산을 수행한다.

- 예를 들어, 덧셈, 뺄셈, 곱셈 등의 산술 연산이나 논리 연산을 처리한다.

5. 데이터 저장 (Data Store):

- 수행한 결과를 적절한 위치에 저장한다.

- 연산의 결과를 레지스터나 기억장치에 다시 기록하여 필요한 경우에 사용할 수 있도록 한다.

명령어 사이클

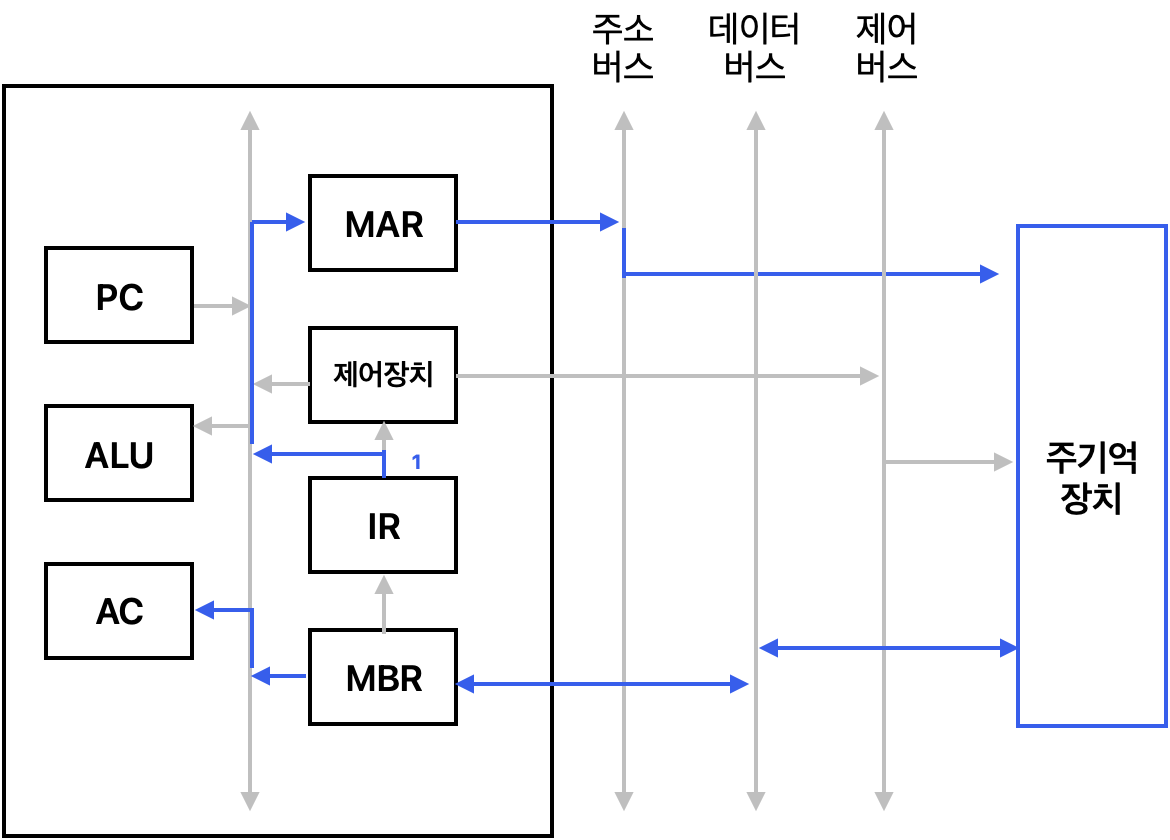

1. LOAD 명령어 실행 사이클:

- 목적: 오퍼랜드 필드에 있는 기억장치 번지의 내용을 Accumulator (AC)로 로드한다.

- 과정:

- MAR ← IR(오퍼랜드): 오퍼랜드 필드에 있는 주소를 MAR로 전송한다.

- MBR ← M[MAR]: 기억장치의 MAR 번지의 내용을 MBR로 읽어온다.

- AC ← MBR: MBR의 내용을 AC로 로드한다.

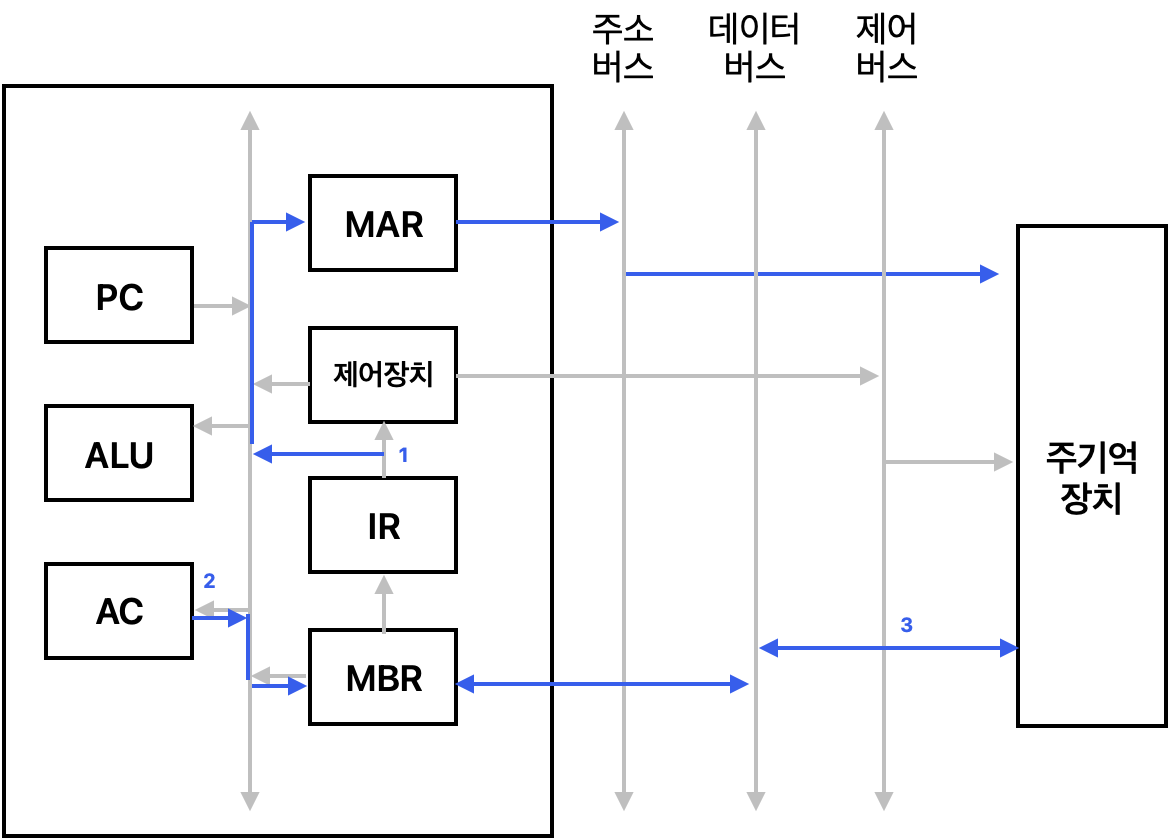

2. STORE 명령어 실행 사이클:

- 목적: Accumulator (AC)의 내용을 오퍼랜드 필드에 있는 기억장치 번지에 저장한다.

- 과정:

- MAR ← IR(오퍼랜드): 오퍼랜드 필드에 있는 주소를 MAR로 전송한다.

- MBR ← AC: AC의 내용을 MBR로 전송한다.

- M[MAR] ← MBR: MBR의 내용을 기억장치의 MAR 번지에 저장한다.

3. ADD 명령어 실행 사이클:

- 목적: Accumulator (AC)의 내용과 오퍼랜드 필드에 있는 번지의 내용을 더하여 AC에 저장한다.

- 과정:

- MAR ← IR(오퍼랜드): 오퍼랜드 필드에 있는 주소를 MAR로 전송한다.

- MBR ← M[MAR]: 기억장치의 MAR 번지의 내용을 MBR로 읽는다다.

- AC ← AC + MBR: AC와 MBR의 내용을 더하여 결과를 AC에 저장한다.

4. JUMP 명령어 실행 사이클:

- 목적: 프로그램의 실행 흐름을 오퍼랜드 필드에 있는 번지로 변경하여 분기한다.

- 과정: PC ← IR(오퍼랜드): 오퍼랜드 필드에 있는 분기 번지를 PC로 전송하여 다음 실행할 명령어 번지를 변경한다.

명령어 파이프라이닝

명령어 파이프라이닝은 CPU의 성능을 향상시키는 기술 중 하나로, 명령어를 여러 단계로 나누어 동시에 처리함으로써 프로그램 처리 속도를 높이는 방법이다. 이러한 기술은 산업 공장의 조립 라인과 유사한 개념을 갖고 있으며, 각 단계는 연속적으로 실행됨으로써 최종 결과를 도출한다.

2단계와 4단계 파이프라인의 구조

2단계 파이프라인: 명령어를 인출하는 단계와 명령어를 실행하는 단계로 구성된다. 각 명령어는 두 단계를 거쳐 실행되며, 인출 단계에서 첫 번째 명령어를 가져오고, 다음 클록 주기에서 실행 단계로 보내어 실행한다. 동시에 다음 명령어를 가져온다.

4단계 파이프라인: 명령어 인출(IF), 명령어 해독(ID), 오퍼랜드 인출(OF), 실행(EX)으로 나뉘어져 있다. 각 단계의 처리 시간이 동일하도록 구성되어야 하며, 각 명령어는 이 네 단계를 거치며 실행된다. 다음 명령어들은 각 단계를 차례대로 거치며 처리된다.

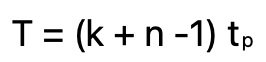

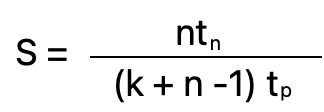

파이프라인의 효율성

- 파이프라인의 효율성은 파이프라인 주기(k), 실행할 명령어들의 수(n), 클록 시간 (t)등에 영향

- 비파이프라인 시스템에서 하나이 명령어를 실행하는데 필요한 시간 tn

- 파이프라인의 이론적 최대 속도 향상률은 파이프라인의 주기 수 k 이다.

파이프라인 도입 전의 한계점

- 명령어 의존성과 해결: 명령어 간의 의존성이 있는 경우, 파이프라인에서는 데이터의 종속성으로 인해 이전 명령어가 완료되기 전에 다음 명령어가 실행될 수 없다. 이로 인해 파이프라인이 멈추게 되고 성능 향상이 어려워진다. 이를 해결하기 위해서는 명령어 스케줄링 및 명령어 재배치 기술 등이 필요하다.

- 브랜치 예측과 예측 실패: 파이프라인에서는 조건부 분기(브랜치)의 경우에도 다음 명령어를 예측하여 실행한다. 그러나 브랜치 예측이 실패하면 파이프라인의 일부가 무효화되어야 하며, 이는 시간 낭비를 야기할 수 있다.

- 메모리 액세스 지연: 메모리 액세스는 파이프라인 성능에 영향을 줄 수 있다. 메모리가 느리거나 액세스 지연이 발생하는 경우 파이프라인이 멈추게 되어 효율성이 저하될 수 있다.

- 하드웨어 구현 복잡성: 파이프라인 구현은 하드웨어 레벨에서 복잡하다. 데이터의 원활한 흐름과 동기화를 유지하는 데 많은 제어와 조정이 필요하다.

- 오버헤드: 파이프라인의 동작을 위한 추가적인 하드웨어, 제어 및 관리를 위한 리소스가 필요하며, 이로 인해 추가적인 오버헤드가 발생할 수 있다.

파이프라인의 저해 요인

- 모든 명령어가 모든 파이프라인 단계를 거치지 않을 수 있다. 몇몇 명령어는 오퍼랜드 인출 등의 특정 단계를 거치지 않을 수 있다. 이러한 경우 파이프라인의 효율성이 저하될 수 있다.

- 두 개의 단계가 동시에 기억장치에 액세스하는 경우에 충돌이 발생할 수 있다. 이러한 충돌은 지연을 일으킬 수 있다.

- 조건 분기 명령어가 실행되면, 이전에 인출한 명령어들이 무효화되어 파이프라인의 효율성이 저하될 수 있다.

김창환 [컴퓨터구조] 복두출판사 p.240~263

'사망년 > 컴퓨터구조' 카테고리의 다른 글

| 버스 중재 방식 (1) | 2023.12.05 |

|---|---|

| 캐시 사상방식 (0) | 2023.12.03 |

| chapter 03 산술과 논리연산 (0) | 2023.09.24 |

| chapter 02 자료 표현 (0) | 2023.09.19 |

| Chapter 01 컴퓨터 시스템 개요 (0) | 2023.09.11 |